# LLM for SoC Security: A Paradigm Shift

Dipayan Saha, Shams Tarek, Katayoon Yahyaei, Sujan Kumar Saha, Jingbo Zhou, Mark Tehranipoor, and Farimah Farahmandi

Department of Electrical and Computer Engineering, University of Florida, Gainesville, FL, USA. Email: {dsaha, shams.tarek, ka.yahyaei, sujansaha, jingbozhou}@ufl.edu, {tehranipoor, farimah}@ece.ufl.edu

Abstract—As the ubiquity and complexity of system-on-chip (SoC) designs increase across electronic devices, the task of incorporating security into an SoC design flow poses significant challenges. Existing security solutions are inadequate to provide effective verification of modern SoC designs due to their limitations in scalability, comprehensiveness, and adaptability. On the other hand, Large Language Models (LLMs) are celebrated for their remarkable success in natural language understanding, advanced reasoning, and program synthesis tasks. Recognizing an opportunity, our research delves into leveraging the emergent capabilities of Generative Pre-trained Transformers (GPTs) to address the existing gaps in SoC security, aiming for a more efficient, scalable, and adaptable methodology. By integrating LLMs into the SoC security verification paradigm, we open a new frontier of possibilities and challenges to ensure the security of increasingly complex SoCs. This paper offers an in-depth analysis of existing works, showcases practical case studies, demonstrates comprehensive experiments, and provides useful promoting guidelines. We also present the achievements, prospects, and challenges of employing LLM in different SoC security verification tasks.

Index Terms—Large Language Model, ChatGPT, GPT-4, Hardware Security, SoC Security Verification, RTL

#### I. INTRODUCTION

The recent rise of Large Language Models (LLMs) has profoundly impacted the field of Natural Language Processing (NLP), ushering in a new era of capabilities and applications. As the size and complexity of these models increase, they consistently improve in performance and efficiency on numerous NLP tasks that span Natural Language Generation (NLG) [1], Natural Language Understanding (NLU) [2] and information retrieval [3]. Specifically, their mastery is evident in fields such as text generation [4], summarization [5, 6], machine translation [7], paraphrasing [8], classification [9], sentiment analysis [10], and question answering [11], to name a few. Beyond their efficacy in such linguistic tasks, LLMs are increasingly showcasing incredible aptitude in complex reasoning tasks. This encompasses arithmetic reasoning [12], commonsense, symbolic, and logical deliberations [13], analogical reasoning [14], and even multimodal reasoning [15]. Such emergent abilities [16], more pronounced in larger models such as GPT-3 [17], GPT-4 [18], PaLM [19], etc., provide a captivating insight into the unforeseen potential of scaled-up language models. Because of zero-shot and fewshot learning capabilities, these pre-trained models (PTMs) are being applied in a wide range of applications: healthcare [20], legal professions [21–23], creative works [24], and robotics [15, 25]. The remarkable success of these PTMs

has catalyzed the development of fine-tuned domain-specific LLMs such as Med-PaLM [26], Med-PaLM 2 [27], PaLM-E [25], BloombergGPT [28], AugGPT [29], LayoutGPT [30], BioBERT [31], SciBERT [32], ClimateBERT [33], etc.

As an example, software programming is witnessing a transformative shift as researchers increasingly incorporate LLMs for diversified coding tasks. Code LLM models [34–43], with their deep understanding of code syntax, semantics, and the intricacies of various programming languages, are being deployed to assist in code generation, completion, translation, explanation, and documentation. Such capabilities streamline the coding process, reduce the margin for human error, and increase overall efficiency. For example, GitHub Copilot [44], based on Codex [35], offers contextual suggestions for multiple programming languages, bridging the gap between human intuition and machine efficiency in software development. Following the remarkable successes in coding assistance, LLMs are expanding their horizons to address the pressing challenges of software security. Recent studies [45–56] demonstrate the ability of LLMs to identify and fix software bugs based on natural language description.

The widespread presence of system-on-chip (SoC) in modern computing systems emphasizes its critical importance. SoCs are now integrated into diverse devices, including smartphones, tablets, IoT devices, and autonomous vehicles, showcasing their significance in the technology landscape. With such an increase in their use, security has become an increasing concern as SoCs collect, analyze, and store users' personal information. Multiple intellectual property (IP) cores with unique functionality and security challenges come together to make an SoC. The extensive functionality coupled with intricate interactions among the IPs, leaves SoCs susceptible to a plethora of security vulnerabilities. From these vulnerabilities, adversaries can exploit information leakage [57, 58], sidechannel leakage [59-61], access control violations [62], etc. The situation is further complicated when considering thirdparty IPs, which are notably prone to issues like hardware Trojans [63]. These issues highlight the importance of thorough security verification in system design. This rigorous and timeintensive process is at odds with the escalating demand for producing billions of computing devices and the corresponding pressure to reduce time-to-market [64]. The tension between these opposing factors makes effective functionality and security verification increasingly difficult, potentially leading to costly spin-offs if issues are discovered post-production. Unfortunately, the existing SoC security solutions [62, 65–69] are not scalable for handling the increasing complexity and di-

1

versity of modern hardware designs, adaptable to new designs and rapidly evolving threat landscape, and comprehensive in addressing hardware vulnerabilities[70, 71].

Given the complexity and diversity of SoC security issues and the proven prowess of LLMs in coding, NLU, and advanced reasoning activities, the idea of integrating LLMs into the SoC security paradigm appears promising. Such an interaction holds the potential to not only address the existing challenges in SoC security but also to pioneer innovative solutions for the future with the help of the emergent abilities of LLMs. Moreover, the hardware security community has recently begun to explore the potential of LLMs for SoC security [72–78]. These endeavors, which target specific individual challenges within hardware security, highlight the promise of LLMs in this domain. Nevertheless, the amount of existing research in this domain is inadequate and the real potential of LLMs in different SoC security tasks is untapped. This is the first of its kind work that addresses this research gap, thoroughly investigating the potential of LLMs in SoC security verification.

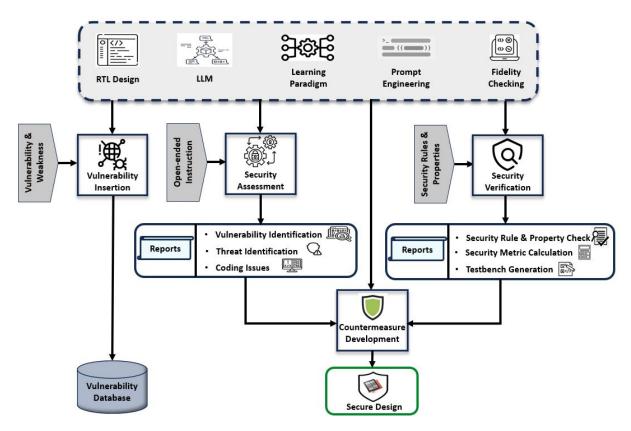

Figure 1 presents a comprehensive illustration of the potential applications of LLM in SoC security, as addressed in this work. The potential of LLM, combined with the proper selection of learning paradigm, the finesse of prompt engineering, and the rigor of fidelity checks, holds the promise of redefining security tasks across domains. Within this context, we explore the following four different security tasks:

- Vulnerability Insertion: We show how adeptly LLM

can introduce potential vulnerability and weakness into

RTL design following natural language description

through the guidance of a well-crafted prompt.

- 2) Security Assessment: Through security assessment, we harness the prowess of LLMs to critically evaluate the security landscape of hardware designs to identify vulnerabilities, weaknesses, and threats through LLM. We also examine the ability of LLM to pinpoint simple coding issues that can turn into security bugs.

- 3) **Security Verification**: In this scenario, we use LLM to verify if the design meets specific security rules or policies. Furthermore, we check the proficiency of LLM in calculating security metrics, understanding security properties, and generating functional testbenches to identify weaknesses.

- 4) Countermeasure Development: In this scenario, we analyze how effectively LLM can mitigate the existing vulnerabilities embedded in the design.

In each of the outlined scenarios, we provide a comprehensive demonstration of executing the tasks using LLMs, with an emphasis on the strategic use of prompt engineering. Through these practical case studies, we establish several strong prompt guidelines specifically applicable to each of the security tasks. In addition, by conducting extensive evaluations, we investigate the proficiency of specific LLMs—particularly GPT-3.5 and GPT-4—in undertaking these four critical security tasks. Our exhaustive discussions and empirical findings not only note the successes of LLMs in the SoC security landscape thus far, but also pinpoint the prospects and prevailing challenges

of employing LLMs in SoC security.

To both the scholarly community and industry professionals, this research work acts as a foundational guide, laying the groundwork for the integration of LLMs in the SoC security landscape. Our exhaustive survey of existing LLMs and related security works not only informs readers of the current state-of-the-art but also explains the evolutionary trajectory of these models, aiding in understanding their capabilities and potential applications in the abovementioned tasks. Our observations and insights through discussions, case studies, and experimentation will help the reader understand the advantages and challenges of employing LLM in SoC security. The comprehensive nature of our investigation opens doors to further exploration, encouraging the community to dive deeper, innovate, and push the boundaries of what is possible, ultimately strengthening the foundations and advancements in hardware security.

The contributions of this work are listed below:

- This is the first of its kind that thoroughly investigates the potential of LLMs in different SoC security-related tasks.

- We provide a comprehensive survey of existing LLMs and related work.

- We first formulate key research questions regarding the prospects of LLM in SoC security and later, systematically analyze them in-depth through practical case studies and large-scale investigation.

- We identify several specific prompt guidelines for using LLM effectively in SoC security-related tasks.

- We identify potential challenges of using LLM in SoC security and also note prospects for further research.

In the remainder of this paper, Section II narrates the preliminaries on SoC security. Later, Section III describes the interaction between LLM and SoC security by providing a comprehensive survey of existing LLMs and different related aspects. Eight research questions addressed in this work are described in Section IV, followed by seven case studies in Section V. Afterward, large-scale investigations on different capabilities of LLM in SoC security-related tasks are discussed in Section VI. Finally, Section VII concludes the paper.

# II. SoC SECURITY

Contemporary SoCs are progressively reaching higher levels of advancement and intricacy. However, this increased complexity also opens up concealed vulnerabilities that attackers can take advantage of. Any bug inside the SoC should be caught and fixed at the earliest stage of the design flow; otherwise, it will be 10 times more expensive than the previous stage. There are rules and guidelines to address the problem of functional bugs in the design-time [79]. The RTL design is the first stage of the design flow in modern ICs. Therefore, being able to detect and mitigate all the possible vulnerabilities at this stage will significantly decrease the security verification time, effort, and cost.

1) Security Vulnerabilities: Hardware security vulnerabilities are the points in design that an attacker could exploit to gain access to a resource with a security-critical value. A vulnerability can appear in the design in the following ways:

Fig. 1. Potential applications of LLM in SoC security.

- Designers' mistsakes: Designers may not fully understand the implications of their choices or make mistakes in the design phase. As a result, they can inadvertently create security vulnerabilities.

- Vulnerabilities through automation tools: As designs move from abstract models to specific implementations, computer-aided design (CAD) tools may unintentionally introduce vulnerabilities during synthesis and optimization [59].

- Malicious Modifications: Rogue designers or third-party IP providers can intentionally introduce vulnerabilities that create backdoors that result in unauthorized access, alterations, and control of the system [59].

- Test and Debug Infrastructure: Sometimes enhancements in control and observation capabilities for testing and debugging can also provide vectors for attackers to violate confidentiality and integrity in the post-silicon stages [58].

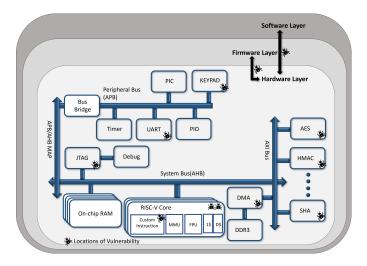

Figure 2 shows the possible locations of the hardware vulnerabilities inside a typical SoC. Many of these hardware vulnerabilities could be prevented or mitigated during design time with a set of guidelines for general hardware description language (HDL) code structures and design practices. The previously discovered vulnerabilities can be utilized for studying the root cause of them in the design and eventually their mitigation. The most relevant work on hardware vulnerability is Common Weakness Enumeration (CWE). It is a community-developed list of hardware and software weaknesses founded by MITRE [80]. CWE offers an initial approach to catego-

rizing various hardware vulnerabilities through a set of three fundamental questions: the underlying reason for including the vulnerability in the design, the timing of its inclusion, and its potential location. The database is continuously maintained through regular assessments of introduced vulnerabilities and is further organized into distinct categories for the user. For example, CWE-1260 specifically addresses issues related to improper memory overlap among protected memory regions. If an application operating at a lower privilege level is intentionally programmed to overlap with an application at a higher privilege level, it can result in a privilege escalation problem, potentially leading to a security breach. While CWE vulnerabilities offer a fundamental understanding of hardware vulnerabilities, they lack benchmarks to validate vulnerable designs.

Another comprehensive resource is the Trust-Hub property database [81]. Additionally, hackathons like Hack@Dac [82] and the HOST Microelectronics Challenge [83] serve as valuable resources for identifying emerging vulnerabilities in SoC designs. However, many of these documented vulnerabilities are either not open-source or lack adequate documentation. The work presented in [84] provides a comprehensive database of SoC vulnerability benchmarks, facilitating the verification of different designs using various verification techniques on a common platform. Nevertheless, there is still room for significant improvement, as new vulnerabilities are continually discovered and can pose significant security risks to hardware designs.

Fig. 2. A typical SoC with probable locations of hardware bugs

- 2) Threat Modeling: Threat modeling in hardware security involves identifying potential adversaries such as hackers, insider threats, competitors, or malicious entities, and the assets they might target, like IP or sensitive data. It assesses attack vectors, including physical attacks, side-channel attacks (e.g., power [61, 85, 86], electromagnetic emission [87], and timing [88]), and software-exploitable hardware attacks [89, 90], and identifies vulnerabilities within the hardware design. This process outlines potential attack scenarios and establishes security requirements for hardware systems. For example, we can explore a particular threat scenario that involves the injection of malicious logic into a design [91]. In this scenario, the threat actor is an employee within a company who possesses database access to the design. This employee exploits their authorized access to introduce harmful code or vulnerabilities into the hardware design or its configuration files. These insider-driven attacks have the potential to establish a hidden entry point that could expose valuable, sensitive information categorized as the assets of the hardware IPs. This threat modeling process helps to outline different attack scenarios or sequences that an attacker might employ to execute his intention. Ultimately, a well-crafted threat model provides the security requisites for any hardware system subject to scrutiny.

- 3) Challenges in Security Verification: The verification process in chip design is a major bottleneck, taking up over 70% of resources and time [92]. Recently, a noticeable increase has also been observed in the instances where the verification process has contributed more than 80% of the total duration of the project [64]. Ensuring secure and compliant SoCs for diverse applications becomes even more challenging, necessitating the identification and addressing of security vulnerabilities in pre-silicon stages. These challenges include the globalized nature of the development lifecycle, complex interactions among hardware, software, and firmware layers leading to unforeseen threats, increased design complexity that limits verification coverage, and the lack of standardized benchmarks for comparing emerging verification techniques. Currently, security verification and validation suffer from limited success due to inadequate prioritization of security in design, lack of suitable threat models and vulnerability databases, and reliance

on mostly manual and ad-hoc security analysis and mitigation methods. The state-of-the-art verification methods for security focus on assertion-based security property verification [93], information flow tracking [94], fuzz testing [95], concolic testing [96], penetration testing [97], and AI-based hardware verification [98]. The following discussion describes recent trends in hardware design verification approaches.

- 1) Assertion-based Security Property Verification: Assertion-based security property verification is a vital method for expediting the validation process of hardware designs. It involves incorporating security-related logical statements, or property-based assertions, into the design of a system to formally define security requirements and constraints during development and testing [93, 99, 100]. This technique addresses a key challenge in hardware validation: the limited observability of designs during testing. Observability deals with the capacity to monitor different states within the design. By integrating these properties, we can enhance the observability of design components, enabling the detection of anomalous behavior during simulation. Moreover, assertions based on these properties can identify errors during simulation, significantly reducing the time and resources required for verification. Two widely used assertion specification languages for this purpose are System Verilog Assertions (SVA) [101] and Property Specification Language (PSL) [102], typically applied at the RTL abstraction level of the design. Automated assertion generation techniques have gained popularity to streamline the process of generating assertions and reduce manual effort [103-105]. However, a key challenge with these methods is ensuring the functional accuracy and coverage of the generated assertions. Additionally, these generated assertions operate at the bit level, which can noticeably extend simulation runtimes.

- 2) **Information Flow Tracking:** Information flow tracking (IFT) within hardware verification is a method utilized for monitoring and regulating the transfer of data or signals within a hardware design or system. Its primary application lies in the domain of security and safety verification, ensuring that sensitive or critical information is managed appropriately and does not unintentionally leak or lead to undesired behavior. IFT effectively identifies and mitigates hardware vulnerabilities, including issues such as timing side channels and hardware Trojans [106, 107]. The most commonly employed IFT techniques include SecVerilog [106], Sapper [108], Caisson [109], and VeriCogIFT [107]. While these approaches excel at detecting hardware bugs associated with information leakage, they are limited by certain problems, such as the need to learn a new language, the requirement for manual annotation, and the inability to distinguish between implicit and explicit information flows. The RTLLIFT approach, as detailed in [110], addresses these challenges by operating directly within existing HDLs and by enabling the differentiation between implicit and explicit flows. Nonetheless, this approach demonstrates

- limitations in terms of performance when dealing with complex designs, compelling designers to make tradeoffs between precision and computational complexity. Additionally, these approaches are not comprehensive enough to detect most of the security vulnerabilities.

- 3) **Fuzzing:** It is a popular testing method in software and has recently attracted a lot of attention in the hardware security verification domain. "Fuzz testing" or "fuzzing" denotes a method involving randomized testing of software programs to identify irregularities and weaknesses [111]. Fuzzing typically involves an automated or semiautomated process designed to check a wide range of predefined (instrumented) scenarios involving invalid inputs, with the aim of triggering any existing vulnerabilities within a program. In the hardware domain, fuzzing has been introduced primarily as a solution to address the scalability challenges associated with formal verification methods [112]. Fuzzing can be classified into black-box fuzzing, gray-box fuzzing, and whitebox fuzzing based on the information available during the verification phase. Black-box fuzzing relies on the design specifications and is effective for designs with limited information about internal signals [113]. Whitebox fuzzing is utilized when the design information is completely available [114], and gray-box fuzzing is a hybrid framework to use the best of both white-box and black-box fuzzing techniques [115]. However, these solutions suffer from several drawbacks, such as limited vulnerability coverage, low accuracy due to limited visibility, and poorly defined coverage metrics [95].

- 4) **Penetration Testing:** Penetration testing involves actively simulating potential attacks to assess the security of a hardware system or device, aiming to discover vulnerabilities and weaknesses [116]. Its primary goal is to evaluate how well hardware components and systems can withstand potential threats and unauthorized accesses. Similar to fuzzing, penetration testing can adopt black-box, white-box, or gray-box approaches based on the specific threat and available resources [117]. This method comprises various stages, ranging from assessing hardware design to exploiting a specific vulnerability that needs resolution. In contrast to random test patterns, penetration testing relies on precise information about security properties, vulnerabilities, and established threat models. However, applying penetration testing in the hardware domain poses greater challenges compared to the software domain because hardware vulnerabilities are more diverse, requiring distinct strategies for different vulnerabilities in each targeted penetration testing scenario [67].

- 5) Concolic Testing: Concolic testing, as an automated test vector generation approach, combines concrete execution with symbolic execution (concolic) to analyze and validate the behavior of a system [118, 119]. This method blends the execution of a program or hardware design, involving actual (concrete) input values, with abstract symbolic representations of input values. The primary objective of Concolic testing is to systematically

- explore different execution paths within a program or hardware design. By incorporating symbolic inputs, it can simultaneously investigate multiple paths, including those that might be challenging to reach using traditional testing methods. Concolic testing can be resource-intensive, particularly when applied to sizable and complex hardware designs or software programs. In recent times, Concolic testing has found application in hardware security verification, serving purposes such as the detection of hardware Trojans [119], the identification of bugs within the CPU core of SoC [120], and firmware validation [121]. Unfortunately, these methods either only work for a certain part of the SoC due to scalability issues or are limited to detecting a few hardware vulnerabilities.

- 6) AI-based Verification: Machine learning (ML) and deep learning (DL) are emerging tools that have recently gained significant attention within the field of hardware verification. ML techniques find applications in diverse verification processes, including the generation of challenging test cases that are hard to achieve and the validation of test results to enhance coverage. Current research trends in this area include creating constraint-random test vectors through supervised and reinforcement learning [122], fine-tuning decision-making procedures for SAT solvers [98], the identification of hardware Trojans [123], and in-depth debugging of system failure analysis [124]. While the prospects are undoubtedly promising, the integration of AI into hardware verification is not without its set of challenges. These hurdles stem from the following factors

- Design dependency: A critical issue often overlooked is the design dependency of AI-based solutions. Due to the lack of a vast and rigorous dataset that involves all corner cases and types of designs, these solutions are often tailored to specific designs and lack adaptability. This limitation hinders their applicability across diverse hardware designs, making them less versatile and effective in a broader context

- Data management: There exists a scarcity of datasets in the hardware security domain that encompass all potential scenarios and corner cases. This data scarcity can lead to the underperformance of ML models that cannot fully optimize the verification process. Lack of benchmark is also a critical challenge for proper evaluation of AI-driven security verification methods.

- Scalability and Efficiency: AI-based solutions are resource-intensive, raising concerns about scalability and efficiency. The time required to train and validate models can be significant, impacting the verification timeline.

- Feature selection and objective function design: There exists a difficulty in identifying and selecting the most relevant features and designing appropriate objective functions for security verification tasks.

In summary, existing verification methods require significant manual labor for security verification, and also suffer from the problems of adaptability and scalability. A notable issue lies in the scarcity of reliable databases for the development of effective techniques and proper evaluation of performance. LLMs hold the potential to introduce creative solutions to address these prevailing challenges in hardware security verification. With proper prompt engineering, LLMs can prove to be highly useful in identifying and mitigating vulnerabilities for complex hardware designs that can reduce a lot of manual effort. Furthermore, the inferential capabilities of LLMs can be harnessed to construct comprehensive databases in the domain of hardware security, which can help solve the problem of lack of data and adaptability in the existing approaches. The incorporation of LLMs can enhance the precision, efficiency, and adaptability of hardware security verification, marking a significant stride toward overcoming existing limitations.

#### III. LLM IN SOC SECURITY VALIDATION

In the preceding sections, we thoroughly explored contemporary SoC security validation solutions and their limitations. Building on that foundation, this section ventures into the captivating intersection of LLMs and SoC security. The synergy between LLM and SoC is a pivotal junction where computational linguistics seamlessly integrates with hardware security. We begin with a thorough survey of the established LLMs to offer insights into their learning settings, evolution, architectures, capabilities, and current state. After setting this foundation, our narrative progresses to a deeper exploration of GPTs, the specialized models designed for coding tasks, and LLM chatbots. Later, we explore the art of prompt engineering, highlighting its significance in refining usermodel interactions for security validation. We then transition to discussions of the APIs associated with LLMs. Afterward, we describe the importance of fidelity checking in LLM-based solutions. Concluding the section, we turn our attention to the existing works adopting LLM for software and hardware security solutions.

#### A. Preliminaries

At first, we narrate three basic concepts, namely learning paradigms, model architectures, and control parameters, that are necessary to understand how LLMs can be incorporated into SoC security validation.

- 1) Learning Paradigms in LLM: As these models evolve, various learning paradigms have been developed to optimize their performance, each with its own set of advantages and challenges. Table I summarizes these methods in terms of data requirement, cost, complexity, and also discusses their role in the context of SoC security. Here, we discuss these learning paradigms and also make our observations in the context of SoC security.

- a) Pre-training: Pre-training serves as the foundation of the LLM learning pipeline. In this phase, the model is trained on a vast corpus of text data to predict the next word in a sentence. This process allows the model to grasp the intricacies of language, from the basic constructs of grammar to the more

abstract concepts of context and semantics. However, while pre-training equips the model with a broad understanding of language, it does not necessarily make the model an expert in specific domains. These pre-trained models can act as foundation models that can be further fine-tuned and adapted to specific domains. BERT [126], GPT-3 [17], LLama-1 [127] are some of these widely used pre-trained models to be named.

In Context of SoC Security: Unfortunately, very few existing pre-trained LLMs used HDL codes in their training corpus which narrows the scope of performing security tasks with LLMs. Pre-training an LLM on a large amount of HDL codes, highly specialized with a focus on security-related tasks, can provide a fundamental understanding of hardware security principles. However, the feasibility of this process in an academic setting is challenging primarily because of its significant computational resources, leading to high costs. There is also a scarcity of a large amount of rich HDL codes to be used for the training. Furthermore, the pre-training process has inherent limitations. The nature of the pre-training data used, typically historical text data, means the model may not be equipped to handle emerging, real-time security threats. This could lead to the model having a potential knowledge gap, as it may not be able to respond to the most recent security threats that it has not been trained on.

b) Fine-Tuning (FT): Pre-trained models in general have a broad understanding of language and context. However, they often require specialized knowledge to excel in specific domains. This is where fine-tuning steps in, refining the parameters of the model to enhance its performance on specialized tasks. Fine-tuning to the LLM can be executed in various ways: supervised fine-tuning, instruction tuning, and reinforcement learning with human feedback (RLHF) [128]. LHF for LLMs combines reinforcement learning and human feedback to fine-tune models. Initially trained on human responses, the model is later optimized using a reward model derived from user feedback. This approach enhances accuracy, reduces biases, and has notably improved models like InstructGPT [129] and ChatGPT [130]. The cost of fine-tuning is typically less than pre-training but still requires significant resources for optimal results This has led to a growing interest in parameterefficient fine-tuning methods [131].

In Context of SoC Security: In relation to SoC security, fine-tuning can have a powerful impact. It can adeptly handle a range of security tasks, from vulnerability insertion and identification to mitigation and security policy generation. However, realizing this potential is not without its challenges. The foremost among these is the significant cost associated with the fine-tuning process. Furthermore, post fine-tuning, models encounter the "knowledge cut-off" dilemma, rendering them oblivious to threats or vulnerabilities that emerge after their last update. This often leads to the need for recurrent fine-tuning sessions. For example, as of today, the number of hardware CWEs listed by The MITRE Corporation [80] is 104. This number is not static—it increases as new vulnerabilities are discovered. Consider a model that has been fine-tuned to recognize and mitigate the existing 104 CWEs. As the list expands with the discovery of new vulnerabilities, the "knowledge cut-off" of the model renders it ineffective against

| Learning Setting                                 | Data Requirement [125]                               | Cost      | Complexity of task | Prospect of SoC Security                                  |

|--------------------------------------------------|------------------------------------------------------|-----------|--------------------|-----------------------------------------------------------|

| Pre-training                                     | >1 trillion tokens                                   | Very High | High               | Not feasible due to high cost and lack of data            |

| Fine-Tuning (Supervised Fine-Tuning)             | 10-100k prompt-response                              | High      | Medium             | Good for all tasks Limited training data & benchmark.     |

| Fine-Tuning (RLHF)                               | Step 1: 100k-1M examples,<br>Step 2: 10-100k prompts | High      | Very High          | Good for vulnerability insertion, detection & mitigation. |

| In-Context Learning (ICL)                        | 2-5 examples                                         | Low       | Low                | Decent at all tasks.  Lack of long term context           |

| Retrieval Augmented In-Context Learning (RA-ICL) | 2-5 examples<br>+ knowledge source                   | Medium    | High               | Decent at vulnerability detection & mitigation            |

TABLE I

PROSPECTS OF SOC SECURITY TASKS FOR DIFFERENT LEARNING SETTINGS OF GPT

these newly identified threats. It is confined to the knowledge it was last updated with, requiring regular fine-tuning to maintain its effectiveness and relevance. Currently, in the domain of SoC security, there exists a potential lack of large datasets for different security tasks which can be for effective fine-tuning. The absence of standardized benchmarks makes objective evaluation challenging for a fine-tuned model.

**Prospect 1:** Fine-tuning can be strategically employed to adapt LLM to specific security tasks, seamlessly bridging the gap between generalized knowledge and domain-specific expertise.

**Challenge 1:** In training LLM for SoC security, a key challenge arises from the limited availability of domain-specific training data and benchmarks, both crucial for refining and validating model performance in specialized security scenarios.

c) In-Context Learning (ICL): In-context learning (ICL), as highlighted in GPT-3 [17], is one of the game-changing capabilities of LLM. ICL, including zero-shot, one-shot, and few-shot learning, allows GPT models to adapt to new tasks bypassing the need for traditional fine-tuning by generating responses based on the instructions supplemented with or without examples. The benefits of ICL are numerous. Firstly, it is adept at broadening its functionality to new tasks using a limited number of examples. Secondly, ICL reduces the requirement for extensive computational resources, making it a more efficient learning approach. Lastly, ICL navigates issues such as overfitting [132] and frequency shock [133], commonly encountered in traditional learning methodologies. In-context learning (ICL) offers benefits but can falter with certain queries due to prompt complexity, quality, and demonstration distribution. These factors play a crucial role in shaping the learning and generalization capabilities of the model.

In Context of SoC Security: In the In-context learning, as applied to the SoC security domain, offers a unique blend of adaptability and specificity. By leveraging the ability of the model to understand and respond based on the provided context, it can offer solutions tailored to specific security challenges. This is particularly beneficial for dynamic security analysis, where the context can vary based on the design, threat landscape, or specific security protocols in place. However, one of the primary challenges is the ability of the model to maintain a long-term context. In SoC security, scenarios

often span complicated designs and complex threat landscapes, requiring a deep and prolonged understanding of the context. If the model struggles to retain or comprehend this extended context, it might offer solutions that are fragmented or lack depth. This limitation could inhibit the model from effectively handling ongoing security scenarios, especially those that require a holistic understanding of the system, its vulnerabilities, and potential mitigation strategies.

**Achievement 1:** ICL in LLMs has revolutionized adaptability, enabling the model to tackle new tasks without traditional fine-tuning, proving particularly beneficial in dynamic security analysis for SoC security.

Challenge 2: ICL can struggle with maintaining a longterm context, especially in complex scenarios like SoC security, leading to potentially fragmented solutions that may not effectively address intricate, ongoing security issues.

d) Retrieval-Agmented In-context Learning (RA-ICL): Pre-trained GPT model does not have access to external knowledge. In order to incorporate up-to-date information that the LLM has not seen during training, it must be retrained. As previously described, ICL also relies solely on the information available during its last training update and may lack the most current information. Retraining these models to update their knowledge is an option but comes with significant costs, both in terms of time and resources. In order to tackle these issues, RA-ICL [134, 135] comes in handy. It addresses these issues by grounding the model during generation by conditioning on relevant documents retrieved from an external knowledge source. Retrieval-Augmented Language Modeling (RALM) systems have two components: knowledge retriever and knowledge generator. The knowledge retriever is responsible for sourcing and retrieving relevant information from an extensive external database, ensuring that the most current and pertinent data is accessed. On the other hand, the knowledge generator takes this retrieved information and integrates it into the response generation process, ensuring that the outputs are not only contextually appropriate but also enriched with the latest information. This approach enriches response generation but might also increase computational complexity and costs.

In Context of SoC Security: In SoC security, retrievalaugmented in-context learning can allow GPT models to pull relevant security information from external databases, enhancing the comprehensiveness and relevance of the security analysis. In a scenario described in Section III-A1b, RA- ICL can solve the problem of "knowledge cut-offs" in the task of hardware vulnerability detection and mitigation. The knowledge retriever component actively can scan and retrieve new CWE data, ensuring that the responses of the model are informed and current.

**Prospect 2:** The adoption of RA-ICL promises enhanced real-time adaptability in SoC security solutions, as it is capable of continuously updating its knowledge base with the most current information, ensuring that responses and solutions are always informed, relevant, and up-to-date.

- 2) Model Architecture: Based on the model architecture, we discuss four categories of existing LLMs: decoder-only, encoder-only, encoder-decoder, and sparse models. A detailed discussion of their structure, working principles, training objectives, functions, and role in the context of hardware design and SoC security is given below.

- a) Encoder-Decoder Model: The most well-known implementation of the encoder-decoder architecture is the transformer, introduced in [136]. This model is a two-part architecture. The encoder processes the input sequence and compresses it into a context or an intermediate representation. The encoder component transforms input tokens into vectors using embeddings and positional encodings, then applies multihead self-attention and feedforward networks. The decoder, starting similarly, incorporates masked self-attention and crossattention with the output of the encoder, ensuring alignment and preventing future word prediction. Sequence-to-sequence models often use this architecture, where the input and output sequences can be of different lengths. These models shine in tasks where there is a direct and complex transformation between inputs and outputs. Examples like machine translation and text summarization are prototypical, as they require the model to understand the input deeply and generate a coherent and contextually accurate output. BART [5], T5 [137], and UL2 [138] are a few well-known encoder-decoder models to be named.

In Context of SoC Security: The encoder-decoder architecture, renowned for its ability in natural language understanding tasks, exhibits versatility in SoC security. Its two-stage process of encoding the input data and then decoding it to produce an output makes it suitable for tasks that require both comprehension and generation. This model is particularly adept at vulnerability mitigation, where understanding the context (encoder) and generating a solution (decoder) are both crucial. However, while it is also a good fit for tasks like vulnerability insertion, security verification, and assessment, it might not always be the optimal choice when the task leans heavily toward either comprehension or generation

b) Decoder-Only: Decoder-only LLMs have established impressive benchmarks in numerous NLP tasks, especially in the generation of free-form text. In a decoder-only model, a sequence is fed into the model, which then directly predicts the next token or word in the sequence. It operates autoregressively, using its generated tokens as context for subsequent predictions. It has two variants: causal decoder and prefix decoder. In a standard decoder (causal decoder), the unidirectional attention masking ensures that a token attends only to previous tokens and itself. Prefix decoders permit

bidirectional attention over prefix tokens while maintaining unidirectional attention to generated tokens. These models excel in tasks like dialog and story generation that require deep input understanding and coherent output generation. Decoderonly architectures, such as the GPT series [17, 18], have gained popularity due to their parameter efficiency, simplicity, generalization, and versatility.

In Context of SoC Security: Decoder-only models, known for their strength in unconditional generation tasks, shine in areas of SoC security that are predominantly generative. They are tailored for tasks like vulnerability insertion, security policy and property generation, and testbench generation, where the model needs to produce new content based on a given prompt or context. For tasks demanding a deeper understanding before generation, like vulnerability mitigation, they can still offer decent performance but might not be the primary choice.

c) Encoder-Only Model: Encoder-only models process input sequences and output a fixed-size context for each token or the entire sequence. These models are adept at distilling information from input sequences into fixed representations, making them suitable for tasks like classification where the aim is to derive a condensed understanding from the input. These models are referred to as "encoder-only" because they prioritize encoding input sequences into meaningful embeddings. The "decoding" they do is not about generating novel sequences (as with autoregressive models), but rather about producing specific outputs from the learned embeddings, such as masked token predictions during pretraining. BERT (Bidirectional Encoder Representations of Transformers) [126] developed by Google and its variants: RoBERTa [139], DistilBERT [140], etc are popular examples. These models have lost popularity in recent times.

In Context of SoC Security: Encoder-only models, with their inherent design to understand and represent data, align well with tasks that require profound analysis. In the SoC security landscape, they are best suited for tasks like security verification and assessment, which demand an in-depth comprehension of the given data without extensive generation. However, when the task requires subsequent generative actions based on the understood context, encoder-only models might not be the ideal choice.

d) Sparse Model: Sparse models, particularly those rooted in the mixture-of-experts (MoE) [141] paradigm, are on the leading edge of LLM architecture innovation. The core idea behind them is to selectively activate only a subset of model parameters for each input, ensuring a more efficient computation without compromising the capacity of the model. In a typical dense neural network, every input engages the full spectrum of the parameters of the model. In contrast, sparse models, and especially those based on the MoE framework, allocate only a specific set of 'expert' parameters tailored for each input. The Switch Transformer [142] and GShard [143] are some of the notable models in this domain. They underline how sparse activation mechanisms can achieve, and sometimes surpass, the efficacy of dense counterparts but with greater computational efficiency.

#### TABLE II

PERFORMANCE OF DIFFERENT MODEL ARCHITECTURES ACROSS VARIOUS SECURITY TASKS. THE "BEST" COLUMN INDICATES THE MODEL TYPE THAT IS MOST SUITED FOR THE TASK, OFFERING OPTIMAL PERFORMANCE. THE "DECENT" COLUMN LISTS MODEL TYPES THAT CAN PERFORM THE TASK REASONABLY WELL BUT MIGHT NOT BE THE OPTIMAL CHOICE. THE "POOR" COLUMN INDICATES MODEL TYPES THAT ARE LEAST SUITED FOR THE TASK AND MIGHT NOT DELIVER SATISFACTORY RESULTS.

| Security Task                            | Performance     |                                 |              |  |  |  |  |

|------------------------------------------|-----------------|---------------------------------|--------------|--|--|--|--|

| Security Task                            | Best            | Decent                          | Poor         |  |  |  |  |

| Vulnerability Insertion                  | Decoder-only    | Encoder-decoder                 | Encoder-only |  |  |  |  |

| Security Verification                    | Encoder-only    | Encoder-decoder<br>Decoder-only | -            |  |  |  |  |

| Security Assessment                      | Encoder-only    | Encoder-decoder<br>Decoder-only | -            |  |  |  |  |

| Security Policy &<br>Property Generation | Decoder-only    | Encoder-decoder                 | Encoder-only |  |  |  |  |

| Testbench Generation                     | Decoder-only    | Encoder-decoder                 | Encoder-only |  |  |  |  |

| Vulnerability Mitigation                 | Encoder-decoder | Decoder-only                    | Encoder-only |  |  |  |  |

In Context of SoC Security: In the context of SoC security, where data can be both vast and intricate, sparse models can provide an optimal balance between computational efficiency and task-specific precision

The potential roles of different model architectures in SoC security tasks are summarized in Table II.

**Prospect 3:** By selecting the optimal model architecture, one can achieve greater precision in executing specific security tasks.

- 3) Control Parameters: One of the benefits of LLM or GPT over other traditional deep learning approaches is that the nature of the generated output can be controlled through several parameters [144]: temperature, top\_p, presence\_penalty and frequency\_penalty. They do not influence the learning process of the model during training. Instead, they are parameters used at inference time when generating outputs from the trained model. A brief definition of these parameters is given below.

- Temperature: It is a parameter that controls the randomness of predictions in the output sequence. When applied to the output probabilities, a high temperature makes the probability distribution more uniform leading to more diverse and potentially more creative output tokens, while a low temperature makes the distribution the distribution more focused resulting in more deterministic and potentially less creative output tokens.

- top\_p: It is an alternative to the temperature used in nucleus sampling, where with this method tokens are selected from the smallest set of top-ranked tokens whose cumulative probability exceeds a certain threshold (p). Lower top\_p values result in a smaller, more focused selection of tokens, which leads to less diverse output.

Indeed, temperature and top\_p serve as crucial parameters in shaping the generation of text or code by LLMs, each influencing the randomness and diversity of the output. For instance, when the goal is to generate alternative versions of a given code segment, a high temperature or top\_p can lead to a range of diverse and innovative solutions. On the contrary, in generating code following a specific pattern or protocol, a lower temperature or top\_p value can help ensure that the resulting code adheres to the desired structure.

*In Context of SoC Security:* These parameters offer promising avenues for exploration and optimization in the context of SoC security. Their manipulation can impact various

tasks related to SoC security, including design generation, vulnerability insertion, security rule and property creation, assertion generation, security assessment, and vulnerability mitigation. However, the optimal setting of these parameters may vary significantly depending on the specific task and the desired balance between creativity and adherence to established patterns or rules. There is a need for a comprehensive investigation of how these parameters should be selected for a particular security task in order to fully leverage their potential in enhancing SoC security.

#### B. Existing LLMs

The introduction of the transformer [136] model has had a profound impact on NLP, leading to significant improvements in performance across a wide range of tasks. The transformer architecture is the foundation for several state-of-the-art models such as BERT [126], GPTs [17, 18, 145, 146]. It is very important to understand the current situation of the development of LLMs. In this light, Table III provides a crucial snapshot of the rapid evolution of LLMs. It offers a consolidated view of various models, highlighting their architectures, training schemes, and unique features. This comprehensive overview will help in making informed decisions about model selection and deployment. For example, by observing trends in model sizes and training techniques, one can anticipate future directions in AI research. We make the following key observations from the table.

- Diverse Developers: While technology behemoths such as OpenAI, Google, and Microsoft lead in terms of the number and variety of LLMs, the emergence of models from organizations like EleutheAI and BigScience showcases the democratization of AI research. The collaboration between Microsoft and NVIDIA for MT-NLG signifies that strategic partnerships can lead to advancements in LLMs.

- Architectural Variations: Decoder-only models seem to dominate the LLM space, indicating their success in tasks related to language generation and completion. The diversity in architectures, with Encoder-Only, Encoder-Decoder, and MoE, indicates ongoing experiments in capturing different facets of language understanding and generation.

TABLE III

A DETAILED OVERVIEW OF EXISTING LLMS SHOWCASING THEIR DEVELOPMENT LINEAGE, ARCHITECTURE, AND UNIQUE CHARACTERISTICS. THE TABLE HIGHLIGHTS THE DEVELOPER, ARCHITECTURE TYPE, BASE MODEL, NUMBER OF PARAMETERS, TRAINING SCHEMES, PUBLIC AVAILABILITY, AND SPECIFIC FEATURES.

| Developer             | Model             | Architecture    | Base<br>Model  | # parameters<br>(B)           | Training<br>Scheme   | Publicly<br>Availability | Remarks                                                            |

|-----------------------|-------------------|-----------------|----------------|-------------------------------|----------------------|--------------------------|--------------------------------------------------------------------|

|                       | GPT-1 [145]       | Decoder-Only    | -              | 0.117                         | Pre-train + SFT      | No                       | Fine-tuning on specific task                                       |

|                       | GPT-2 [146]       | Decoder-Only    | -              | 1.5                           | Pre-train            | No                       | Multi-tasking and zero-shot setting                                |

|                       | Codex [35]        | Decoder-Only    | GPT-3          | 12                            | FT                   | No                       | Code generation and other coding tasks                             |

| Open AI               | GPT-3 [17]        | Decoder-Only    | -              | 175                           | Pre-train +<br>ICL   | No                       | Few-shot learning setting                                          |

|                       | WebGPT [147]      | Decoder-Only    | GPT-3          | 175                           | FT                   | No                       | Long-form question-answering                                       |

|                       | InstructGPT [129] | Decoder-Only    | GPT-3          | 175                           | RLHF                 | No                       | Fine-tuning with human feedback                                    |

|                       | GPT-4 [18]        | Decoder-Only    | -              | -                             | IT +RLHF             | No                       | Remarkable improvement in complex task                             |

|                       | RoBERTa [139]     | Encoder-Only    | BERT           | 0.125 (base)<br>0.355 (large) | Pre-training         | Yes                      | Based on BERT but with different<br>hyperparameter choices         |

|                       | BART [5]          | Encoder-Decoder | -              | 0.140 (base)<br>0.400 (large) | Pre-training<br>+ FT | No                       | Particularly effective when fine-tuned for text generation         |

| Meta                  | NLLB [148]        | MoE             | -              | 54.5                          | Pre-training         | Yes                      | Machine translation over 202 languages                             |

|                       | LLama-1 [127]     | Decoder-Only    | -              | 65                            | Pre-training         | Yes                      | Open language model                                                |

|                       | LLama-2 [149]     | Decoder-Only    | -              | 7-70                          | Pre-training         | Yes                      | LLama-2-Chat though SFT<br>and RLHF on LLama-2                     |

|                       | Galactica [150]   | Decoder-Only    | -              | 120                           | Pre-training         | Yes                      | Trained on corpus of scientific knowledge                          |

|                       | OPT [151]         | Decoder-Only    | -              | 175                           | Pre-training         | Yes                      | Open pre-trained transformer                                       |

|                       | OPT-IML [152]     | Decoder-Only    | OPT            | 30, 175                       | IT                   | Yes                      | Instruction-tuning for generalisation                              |

|                       |                   | -               | 011            | 0.110 (base)                  |                      |                          |                                                                    |

|                       | BERT [126]        | Encoder Only    | -              | 0.340 (large)                 | Pre-training         | Yes                      | Good for language understanding tasks                              |

|                       | XLNet [153]       | Encoder-Only    | Transformer-XL | 0.110 (base)<br>0.340 (large) | Pre-training         | Yes                      | Combination of ideas of BERT and traditional autoregressive model  |

|                       | AlBERT [154]      | Encoder-Only    | BERT           | 0.011 (base)                  | Pre-training         | Yes                      | Improves parameter-efficiency                                      |

| Google                | T5 [137]          | Encoder-Decoder | -              | 11                            | Pre-training<br>+ FT | Yes                      | Transfer learning for NLP                                          |

| Research              | UL2 [138]         | Encoder-Decoder | -              | 20                            | Pre-training         | Yes                      | Different training objective                                       |

| Research              | mT5 [155]         | Encoder-Decoder | T5             | 13                            | Pre-training<br>+ FT | Yes                      | Multilingual variant of T5                                         |

|                       | Flan-T5 [156]     | Encoder-Decoder | T5             | 11                            | FT                   | Yes                      | Instruction fine-tuning on T5                                      |

|                       | Gshard [143]      | MoE             | -              | 600                           | Pre-training         | No                       | Scaling up multilingual translation                                |

|                       | LamDA [157]       | Decoder-Only    | -              | 137                           | FT                   | No                       | Specialized for dialog                                             |

|                       | FLAN [158]        | Decoder-Only    | LamDA-PT       | 137                           | FT                   | No                       | Uses instruction fine-tuning                                       |

|                       | PaLM [19]         | Prefix Decoder  | -              | 540                           | -                    | No                       | Pipeline free training on large scale                              |

|                       | Minerva [159]     | Decoder-Only    | PaLM           | 540                           | Pre-training<br>+ FT | No                       | LLM for quantitative reasoning problem,<br>especially math problem |

|                       | Flan-PaLM [156]   | Prefix Decoder  | PaLM           | 540                           | FT                   | No                       | Uses different instruction fine-tuning                             |

|                       | D I M 2 [1(0]     | D.C.D. I        |                |                               | D                    | N                        | Multilingual & reasoning capabilities                              |

|                       | PaLM 2 [160]      | Prefix Decoder  | -              | -                             | Pre-training         | No                       | Smaller in size but compute-efficient                              |

|                       | AlphaCode [34]    | Encoder-Decoder | -              | 41                            | FT                   | No                       | System for code generation                                         |

| DeepMind              | Chinchilla [161]  | Decoder-Only    | -              | 70                            | FT                   | No                       | Compute-optimal model over Gopher                                  |

| Deeplyllild           | Sparrow [162]     | Decoder-Only    | Chinchilla     | 70                            | SFT+RLHF             | No                       | Information-seeking dialogue agent                                 |

|                       | Gopher [163]      | Decoder-Only    | =              | 280                           | -                    | No                       | Compares Dialogue-Prompted Gopher<br>and Dialogue-Tuned Gopher     |

| ) C                   | DialogGPT [164]   | Decoder-Only    | GPT-2          | 0.117,0.345,<br>0.762         | Pre-training         | Yes                      | Generates conversational responses                                 |

| Microsoft             | DeBERTa [165]     | Encoder-Only    | -              | 0.1 (base)                    | Pre-training         | Yes                      | Improves BERT and RoBERTa                                          |

|                       | DeBERTaV3 [166]   | Encoder-Only    | DeBERTa        | 0.086                         | Pre-training<br>+FT  | Yes                      | Improves DeBERTa                                                   |

| Microsoft<br>& NVIDIA | MT-NLG [167]      | Decoder-Only    | -              | 530                           | Pre-training         | No                       | Comparable to GPT-3 but larger                                     |

|                       | GPT-Neo [168]     | Decoder-Only    | GPT-3          | 1.3                           | Pre-training         | Yes                      | Not fine-tuned for downstream tasks                                |

| EleutheAI             | GPT-J 6B [169]    | Decoder-Only    | -              | 6                             | Pre-training         | Yes                      | Not fine-tuned for downstream tasks                                |

|                       | Pythia [170]      | Decoder-Only    | -              | 12                            | Pre-training         | Yes                      | Not fine-tuned for downstream tasks                                |

| 4 701 7 3             | Jurassic-1 [171]  | Decoder-Only    | -              | 178                           | Pre-training         | Yes                      | Comparable to GPT-3                                                |

| AI21 Labs             | Jurassic-2 [172]  | Decoder-Only    | -              | -                             | -                    | No                       | Capable of composing human-like text                               |

| Yandex                | YaLM [173]        | Decoder-Only    | Megatron-LM    | 100                           | Pre-training         | Yes                      | Focuses Russian and English text                                   |

|                       |                   | -               |                |                               |                      |                          | Fundamentally based on GPT-3                                       |

| TII                   | Falcon [174]      | Decoder-Only    | -              | 40                            | Pre-training         | Yes                      | Falcon-40B-instruct is fine-tuned o                                |

| BigScience            | BLOOM [175]       | Decoder-Only    | -              | 176                           | Pre-training         | Yes                      | Trained on 46 languages and 13 programming languages               |

|                       | BLOOMZ            | Decoder-Only    | BLOOM          | 176                           | FT                   | Yes                      | Zero-shot task generalization abilities                            |

| Others                | GLM [176]         | Decoder-Only    | -              | 130                           | Pre-training         | Yes                      | Bilingual pre-trained LLM                                          |

- **Training Schemes:** Evolving training methods, including RLHF, highlight the industry's push towards refining model outputs using human feedback.

- Model Size: As technology advances, there is a clear trend towards building larger models. However, models like PaLM 2 are emphasized as compute-efficient, highlighting the importance of balancing size with practicality and resource constraints.

- Public Availability: Some models, especially those developed by tech giants like OpenAI, remain proprietary.

Ont he other hand, openly available models, like LLama by Meta or BERT by Google, have spurred a plethora of research, with many in the community building upon or fine-tuning these models for specific tasks.

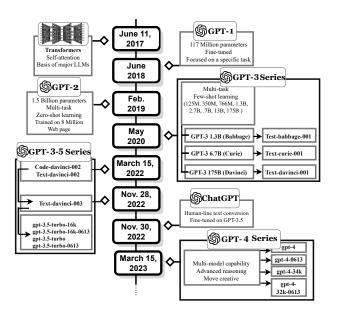

Fig. 3. Timeline for the evolution of GPTs.

#### C. Evolution of GPT

The Transformer [136] model revolutionized NLP by introducing attention mechanisms, eliminating the need for recurrent or convolutional layers. This architecture paved the way for the OpenAI GPT series. GPT-1 [145], launched in 2018, was a breakthrough in language modeling with 117 million parameters. GPT-2 [146], with 1.5 billion parameters, improved coherence in text generation, but had concerns about misleading information. Later, GPT-3 [17], introduced in 2020 with a massive 175 billion parameters, achieved near-human text generation and exhibited "few-shot learning," although it still had some limitations. Subsequent models, GPT-3.5 and GPT-4, further refined these capabilities, addressing previous limitations and setting new benchmarks in the field. The GPT-3.5 series includes models such as 'gpt-3.5-turbo' and its variants, with token limits up to 16,384. Some of these models are chat-optimized, while others, like 'text-davinci-003' and 'text-davinci-002', are superior in language tasks. The Codex model, 'code-davinci-002', is optimized for code completion. Lastly, the GPT-3 series also encompasses models like 'davinci', 'curie', 'babbage', and 'ada', all with a token limit of 2,049. These models vary in efficiency, speed, and cost, with some being also available for fine-tuning. Within the GPT-4 series, there are models like 'gpt-4', 'gpt-4-0613', 'gpt-4-32k', and 'gpt-4-32k-0613', all having a maximum token limit ranging from 8,192 to 32,768. These models are advanced, with some versions optimized for chat, and others offering extended context lengths. A timeline of the evolution of the GPTs is shown in Figure 3.

**Achievement 2:** GPT models, especially GPT-4, stand superior to other counterparts due to their unparalleled understanding of both natural language and codes, combined with their emerging reasoning abilities, marking a remarkable shift in the domain.

*Challenge 3:* High cost associated with GPT models hinders their widespread adoption for large-scale hardware design.

**Challenge 4:** The proprietary designs of GPT models are not open-sourced, limiting researchers and developers from understanding their intricacies and functionalities to conducting fundamental research in the domain.

#### D. LLM for Coding Task

LLMs have shown impressive capabilities in coding tasks, bridging the gap between natural language processing and software development. Over the past few years, they have emerged as invaluable tools for developers, streamlining various stages of the software life cycle. From code generation, defect detection, and auto-documentation, to assisting in debugging and even predicting potential software vulnerabilities, LLMs have transformed traditional coding paradigms. Various finetuned LLMs specially dedicated to coding tasks have been released by fine-tuning pre-trained models. Table IV lists all such code LLMs developed in recent years. Analyzing the table, a few key observations emerge. Firstly, the LLMs have predominantly been developed with a focus on mainstream programming languages like Python. This emphasis on Python and similar languages is understandable given their widespread use in software development and data science. However, this has inadvertently led to a gap in the landscape of LLMs specifically fine-tuned for HDL such as Verilog and VHDL. Second, a significant number of these models have undergone fine-tuning, underscoring the importance of domain-specific training for coding tasks.

In Context of SoC Security: There is a noticeable scarcity of fine-tuned LLMs in Verilog, indicating a potential gap in the handling of HDL. However, given that these models already possess a foundational understanding of coding constructs and logic, there is a promising avenue to further fine-tune them for HDLs, leveraging their inherent coding expertise. this potential fine-tuning becomes even more significant. HDLs play a pivotal role in designing and verifying hardware components, making them crucial in ensuring the security and reliability of integrated circuits and systems. By adapting codecentric LLMs to better understand and generate HDL code, we can harness their capabilities to detect vulnerabilities, suggest mitigations, and even aid in the design of secure hardware components, thus bolstering the overall security posture of SoC designs.

**Achievement 3:** LLMs have made remarkable strides in understanding and generating mainstream software programming languages, transforming traditional software development paradigms.

**Challenge** 5: The current landscape of LLMs is predominantly tailored for mainstream programming languages, leading to a gap in specialized models for HDLs.

**Prospect 4:** There is a promising avenue to fine-tune existing code-centric LLMs, which are proficient in mainstream programming languages, for HDLs to bolster SoC security.

#### E. LLM for Chatbot

The evolution and diversity in the development of LLMs for chatbot applications are clearly evident from Table V.

TABLE IV

A COMPREHENSIVE LIST OF LLMS SPECIFICALLY DEVELOPED FOR CODING TASKS. THE TABLE PROVIDES INSIGHTS INTO THE EVOLUTION AND DIVERSITY OF CODE-CENTRIC LLMS, EMPHASIZING THE VARIED APPROACHES AND INNOVATIONS TAILORED FOR CODE GENERATION, UNDERSTANDING, AND OTHER CODE-RELATED TASKS.

| Code LLM                  | Model<br>Architecture          | Parameters     | Training                           | Base<br>Model           | FT for<br>HDL? | NL+<br>Code | Open/<br>Closed | Task Paradigms                                                                                                                  |

|---------------------------|--------------------------------|----------------|------------------------------------|-------------------------|----------------|-------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------|

| AlphaCode [34]            | Encoder-<br>Decoder            | 1B (base)      | Pre-training<br>+ FT               | -                       | No             | Code        | Closed          | Code generation                                                                                                                 |

| CodeBERT [42]             | Encoder-Only                   | 125M           | Pre-trained                        | RoBERTa<br>-base        | No             | NL+Code     | Open            | Code search and code-to-<br>documentation generation                                                                            |

| CodeGeex [41]             | Decoder-Only                   | 13B            | Pre-training<br>+ FT<br>+ Few-shot | -                       | No             | NL+Code     | Open            | Pre-trained, fine-tuned &<br>few-shot prompted model<br>performs code generation,<br>translation & explanation,<br>respectively |

| CodeGen-Mono [36]         | Decoder-Only                   | 350M-<br>16.1B | Pre-Training<br>+ FT               | CodeGen<br>-Multi       | No             | NL+Code     | Open            | Code generation                                                                                                                 |

| CodeGen-Multi [36]        | Decoder-Only                   | 350M-<br>16.1B | Pre-Training<br>+ FT               | CodeGen<br>-NL          | No             | NL+Code     | Open            | Code generation                                                                                                                 |

| CodeGen2.5-Multi [37]     | -                              | 7B             | Pre-Training<br>+ FT               | -                       | No             | NL+Code     | Open            | Code generation and in-filling                                                                                                  |

| Code LLama [177]          | Decoder-Only                   | 7, 13 & 34     | FT                                 | LLama-2                 | No             | NL+Code     | Open            | Code generation and understanding                                                                                               |

| Code LLama-Python [177]   | Decoder-Only                   | 7, 13 & 34     | FT                                 | Code LLama              | No             | Python Code | Open            | Specialized for Python                                                                                                          |

| Code LLama-Instruct [177] | Decoder-Only                   | 7, 13 & 34     | IT                                 | Code LLama              | No             | Code        | Open            | Code generation and understanding                                                                                               |

| CodeT5 [178]              | Encoder-Decoder                | 60M,<br>220M   | Pre-Training<br>+ FT               | T5                      | No             | Code        | Open            | Code understanding and generation tasks                                                                                         |

| CodeT5+ [179]             | Encoder-<br>Decoder            | 220M-<br>16B   | Pre-Training                       | T5/<br>CodeGen<br>-Mono | No             | Code        | Open            | Code understanding (retrieval,<br>defect and clone detection) and<br>summarization, generation                                  |

| Codex [35]                | Decoder-Only                   | 12B            | FT                                 | GPT-3                   | No             | Code        | Closed          | Generation and others                                                                                                           |

| Incoder [180]             | MoE                            | 6.7 B          | Pre-training                       | FairSeq                 | No             | NL+<br>code | Open            | Generation, masking<br>and infilling                                                                                            |

| JuPyT5 [181]              | Encoder-Decoder                | 350 M          | Pre-Training                       | BART                    | No             | Code        | Closed          | Code in-filling                                                                                                                 |

| LongCoder [182]           | Long-Range<br>Transformer      | 150M           | Pre-Training                       | UnixCoder               | No             | Code        | Closed          | Code complition                                                                                                                 |

| PanGu-Coder [183]         | Decoder-Only                   | 317M<br>2.6B   | Pre-training                       | PANGU-                  | No             | Code        | Closed          | Text-to-code generation                                                                                                         |

| PanGu-Coder2 [43]         | Decoder-Only                   | 15B            | RRTF<br>(Evol-Instruct)            | -                       | No             | Code        | Closed          | Code generation                                                                                                                 |

| PLBART [184]              | Encoder-<br>Decoder            | 140M           | Pre-training<br>+FT                | BART                    | No             | NL+<br>Code | Closed          | Summarization, generation,<br>translation and classification                                                                    |

| PolyCoder [185]           | Decoder-Only                   | 2.7B           | Pre-Training                       | GPT-2                   | No             | Code        | Open            | Code generation                                                                                                                 |

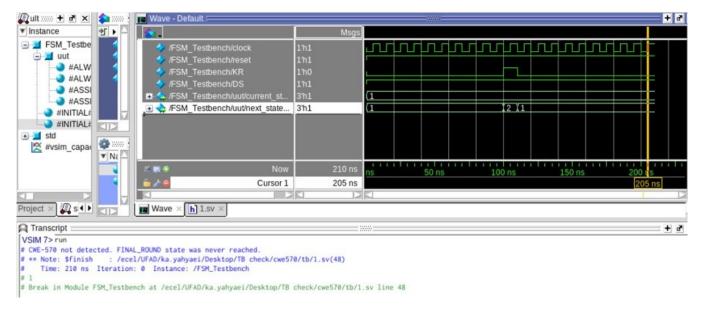

| SantaCoder [186]          | Decoder-Only<br>with FIM & MQA | 1.1 B          | Pre-training                       | -                       | No             | Code        | Open            | Infilling capabilities                                                                                                          |